解決先進應用晶片的挑戰: 兼顧安全與可靠度的創新記憶體(SRAM)修復技術

因應AI與DPU架構的高速發展,SRAM 容量需求急速攀升

當物聯網、行動裝置與邊緣運算大行其道之時,隨著 AI 的蓬勃發展,各項應用裝置逐漸開始導入大量的 AI 應用,例如智慧型感測,車載駕駛輔助 (ADAS),語音辨識等等,都會需要載入越來越大型的訓練模型 (Model) 。另一方面,隨著CPU效能進步的趨緩,用來降低IO並分層資料處理的DPU應用或 PIM (Process in Memory) 架構隨之盛行。然而,分層處理的CPU越多,也需要更大量的SRAM作為快取記憶體 (CACHE) 來服務高速的 CPU。也就是說, AI 應用以及DPU架構的高速發展將促使SRAM 的容量需求不斷成長。

隨著先進製程的發展,SRAM 良率與可靠度面臨的挑戰

SRAM 是CMOS技術進展的驅動力。隨著AI應用崛起,晶片上的SRAM數量將飆升至數十到幾百MB。原則上,SRAM 的容量(density)越大,產生壞Bit Cell的機率就越高,良率(yield)就面臨了挑戰。除此之外,隨著製程技術的發展,還帶來了其他可能的挑戰:

其一是隨著最新CMOS技術進展,即使到了FinFET世代,因為黃光與蝕刻技術尚無法做到隨著摩爾定律(Moore’s Law)等比例縮小,如電晶體通道或金屬跑線的長度 (Channel Length) 和週距 (Pitch) 等,使得SRAM 記憶體單元大小的微縮預期越來越低。

其二是隨著製程微縮與電晶體密度上升,電晶體工作功耗的產生造成溫度上升,進而造成電晶體的靜態漏電流上升,導致SRAM 安全工作區間 (SNM, Static Noise Margin) 下降。

基於以上種種SRAM良率和可靠度的挑戰,如何修復SRAM 便成為相當重要的課題。

了解記憶體修復背後的機制

記憶體修復技術基於將冗餘行或列新增至記憶體陣列,以便在需要時能以備用的冗餘單元取代有缺陷的主記憶體單元。因此,即使嵌入式記憶體本身陣列在製造過程中產生了部份缺陷,也能以此方式修復,不需要丟棄整個晶片造成成本浪費。

最初,測試、分析和修復記憶體的過程是手動執行的,需要使用額外的設備,例如外部記憶體測試機台。然而,隨著晶片變得更加複雜、測試時間更長,人們開始尋求改進以加快測試流程,其中一項創新便是內建自檢 (BIST) 和修復 (BISR) 單元的開發。與手動修復記憶體的過程相比,記憶體BISR (MBISR)使診斷和修復變得測試儀的更加容易。自動導入測試並執行修復,不僅節省了時間、金錢和設備資源,過往外部記憶體測試儀的頻寬限制也不復存在。

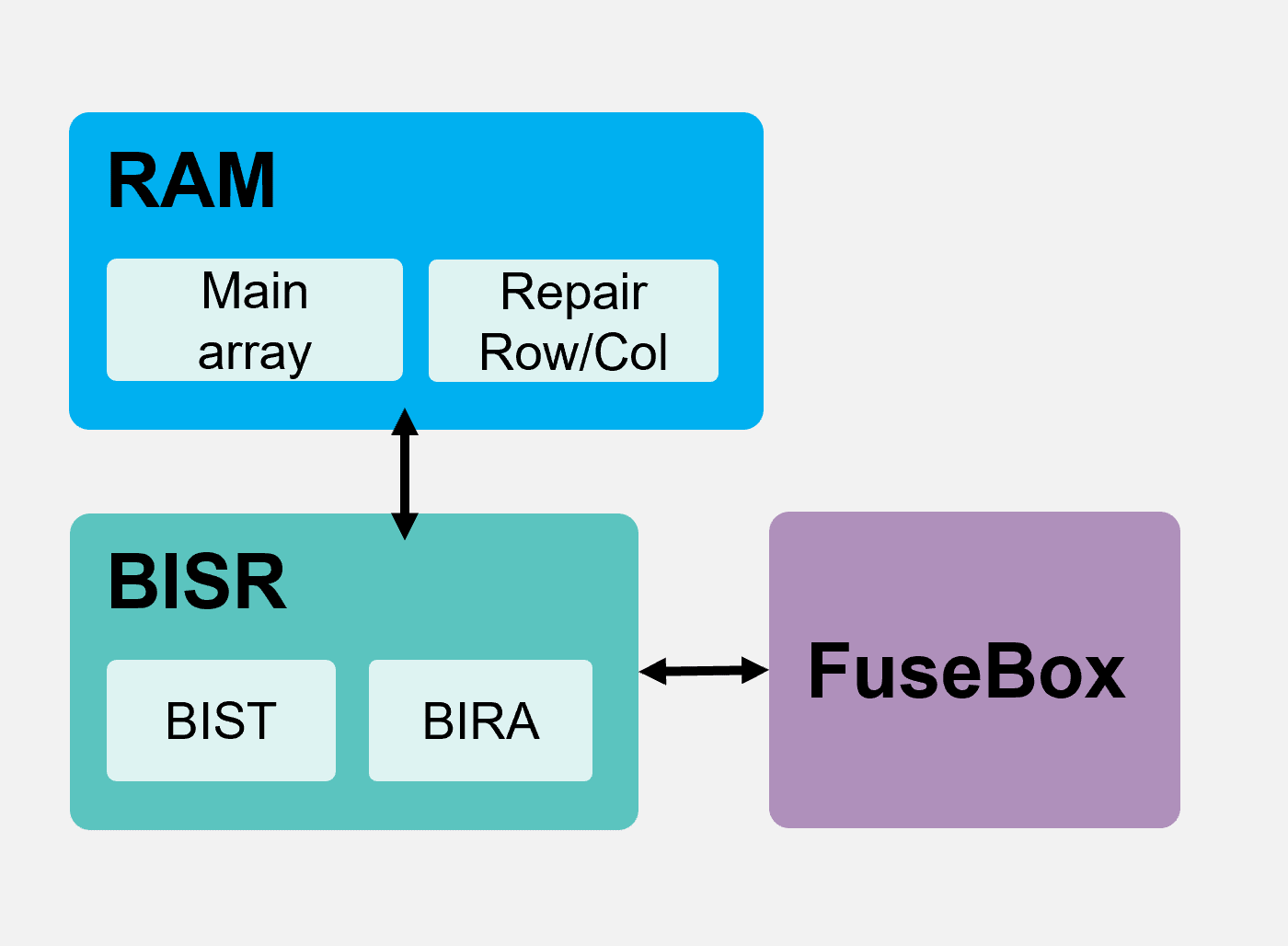

典型的MBISR設定由內建測試 (MBIST)、修復分析 (MBIRA)和FuseBox模組組成。BIST模組測試主儲存單元和備用儲存單元,以識別儲存單元是良好或是有缺陷。MBIRA 模組則負責分配良好的備用單元來替換已標記為有缺陷的主記憶體單元。修復分析完成後,此記憶體陣列「修復簽章」的永久記錄將寫入專用記憶體(通常稱為FuseBox)中。

圖1: MBISR 功能組成示意圖

為什麼OTP是更好的選擇?

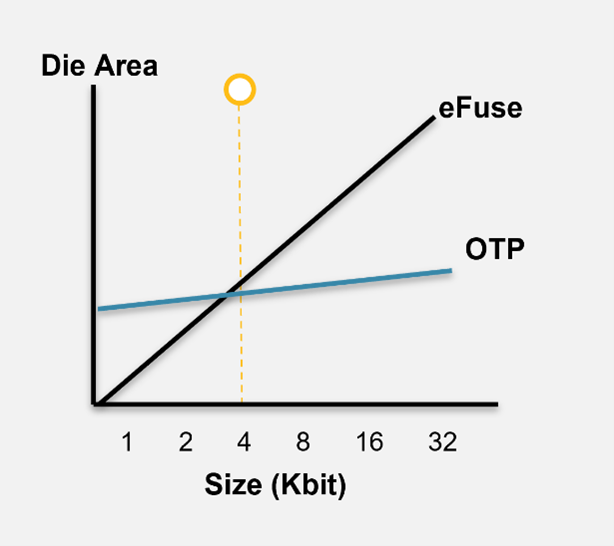

最早的FuseBox是一組金屬保險絲,透過使用大電流將保險絲熔斷來存放修復簽章。DFT tool 原本也僅使用 eFuse做記憶體修復。隨著技術演進,當AI應用越來越複雜,需要的SRAM 容量越大,需要修復的 SRAM 容量也隨之增加。在7nm 以下製程的AI 應用中,SRAM 容量已經到達幾十到幾百MB,而需要修補的SRAM容量已經是幾十到幾百 Kb以上,所以至少需要幾十到百Kb的FuseBox 來儲存。此時,透過反熔絲(Anti-fuse)技術來實現Fusebox功能的一次性可編程記憶體(OTP)成為了更好的選擇,特別是在先進製程上。為什麼呢?以下用力旺電子的NeoFuse (Anti-fuse OTP)與eFuse來做比較。

在先進製程中,力旺電子的NeoFuse OTP與eFuse相比有以下幾大優勢:

1、面積優勢: NeoFuse在幾百Kb 容量的應用上,面積遠小於 eFuse

2、可靠度: NeoFuse沒有讀取限制,擁有最高的可靠度

3、量產良率: NeoFuse在大容量擁有最好的良率與量產紀錄

4、設計簡便:毋需考量提供大電流路徑的特殊電路設計,能簡單布局與滿足終端寫入的便利性。

總結而言,NeoFuse 在需求容量愈大的應用上,尺寸和良率的優勢會愈加顯著。

圖2: OTP和eFuse容量與尺寸關係示意圖

為先進應用同步考量安全操作與記憶體修復的解決方案

隨著先進應用的發展,SRAM修復的需求急遽增加,其安全部署亦不容忽視。力旺電子及其子公司熵碼科技是記憶體解決方案和晶片安全的領先廠商,將FuseBox功能合併到其硬體信任根解決方案中,不僅可以節省系統面積,還可以節省設計成本/精力,以一個解決方案同時履行安全操作和SRAM修復的功能。

事實顯示信任根被廣泛地指定為安全架構中的標準元件,例如Arm的機密運算架構、RISC-V的Keystone可信任執行環境(TEE)、PSA Certified的物聯網安全框架以及錨定統一可延伸韌體介面 (UEFI) 的安全啟動流程等安全架構皆以信任根作為其基底。

結論

在AI的蓬勃發展下,SoC需要更高的運算能力,透過多核心處理器和高SRAM密度來處理大量資料。然而先進製程對SRAM帶來的良率及可靠度挑戰,其高昂的成本更凸顯了SRAM修復能力的重要性。同時,隨著先進應用對安全性的要求,能整合這兩項需求的解決方案對晶片設計工程師而言無疑是更好的選擇。力旺和熵碼的安全解決方案採用在良率、尺寸上皆優於eFuse的NeoFuse,更設計了完整的MBSIR工具以節省工程師的設計資源,幫助半導體產業迎向這個對安全運算和記憶體需求更上層樓的時代。