DDR5

Introducing DDR5 (Double Data Rate 5), the latest generation of dynamic random-access memory (DRAM) that offers higher data transfer rates, increased bandwidth, and enhanced power efficiency.

DDR5 is designed to meet the demands of modern computing systems and emerging applications, such as AI and data centers. With faster speeds starting at 3200 MT/s, DDR5 enables quicker data access and processing, resulting in improved system performance.

It also provides significantly higher bandwidth, facilitating efficient data communication between memory and system components. This is crucial for data-intensive tasks, such as real-time analytics, multimedia processing, and complex simulations.

DDR5 incorporates advanced power management techniques, reducing power consumption and supporting environmental sustainability. Backward compatibility ensures seamless integration with DDR4 systems.

DDR5 is set to revolutionize industries such as data centers, gaming, and AI with its improved performance, efficiency, and compatibility.

Multi-Times Programmable Solutions for Latest DDR5 DIMM Module

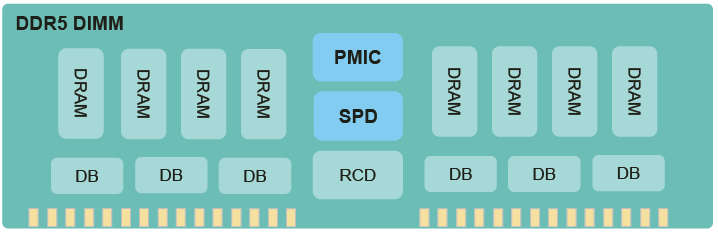

For DDR5 DRAM, a dedicated PMIC for supplying power to the DIMM has been added on the DRAM module. The on-DIMM PMIC provides more efficient and reliable power management to support the high-speed operation of DDR5 memory. This PMIC usually requires few Kilobits MTP to store configurations, the multiple-times programmability provides module manufacturers with greater flexibility to fine-tune the power configurations. eMemory’s NeoEE and NeoMTP are both excellent choices for this application.

In addition, the legacy SPD (Serial Presence Detect) EEPROM for DRAM module now integrates more features like temp. sensor and hub-functions to monitor environment temperature and communicate with the system via I2C/I3C. The EEPROM is for storing information and parameters pertaining to the DIMM, DRAMs and other on-DIMM devices. NeoEE is very suitable to SPD due to the 100K times endurance requirements.

Diagram of DDR5 DIMM Module

Reliable and High-Endurance

FN tunneling is an ideal mechanism to program or erase the NVM cell with low power operation while building comparatively low stress over the memory cell. NeoEE utilize FN tunneling for both PGM/ERS operations therefore cause the least degradation to the gate oxide compared to other MTP technologies. Up to 100K times write cycles is mandatory for the SPD chip according to JEDEC standards. Therefore, NeoEE is the best choice for SPD application.

Wide availability and Field Programmability

eMemory’s NeoEE is available in standard logic process platforms with no additional masks and available on specialty processes like HV/BCD platforms. Meanwhile, field programmability further provides more flexibility for customers to configure their chips in different production stage and even for end-users to rewrite the settings after shipping.

Customizable for Design Flexibility

eMemory’s NeoEE IP can be customized to fulfill different design requirements. E.g., single or dual power supply, wide-range power supply, metal routing customization, substrate isolation...etc. Optional features like byte/word/page program and erase, ECC blocks, customized I/O bandwidths, and even resizable memory units can be discussed. Our wide-available “eNVM gadgets" provides obvious value for customers with great design and manufacturing flexibility.